2021年第一季度,中國上市保險(xiǎn)公司整體業(yè)績呈現(xiàn)明顯的“高開低走”態(tài)勢。在經(jīng)歷了年初開門紅的高光表現(xiàn)后,后續(xù)增長動(dòng)力不足,保費(fèi)收入增速明顯放緩,反映出行業(yè)面臨的結(jié)構(gòu)性挑戰(zhàn)。

一、業(yè)績表現(xiàn):高開低走成普遍現(xiàn)象

從已披露的數(shù)據(jù)看,主要上市險(xiǎn)企一季度新單保費(fèi)普遍呈現(xiàn)前高后低趨勢。1月份借助“開門紅”營銷活動(dòng)實(shí)現(xiàn)快速增長,但2-3月份增速明顯回落。其中,壽險(xiǎn)業(yè)務(wù)首年期交保費(fèi)增速放緩尤為明顯,反映出客戶需求疲軟和市場競爭加劇的雙重壓力。

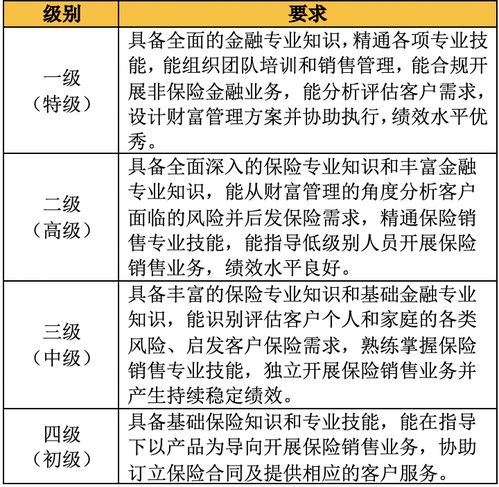

二、代理人隊(duì)伍質(zhì)態(tài)提升迫在眉睫

在當(dāng)前市場環(huán)境下,傳統(tǒng)人海戰(zhàn)術(shù)已難以為繼。代理人隊(duì)伍規(guī)模持續(xù)收縮的同時(shí),人均產(chǎn)能提升緩慢成為制約行業(yè)發(fā)展的瓶頸。數(shù)據(jù)顯示,主要險(xiǎn)企代理人數(shù)量較去年同期普遍下降10%-20%,但人均新單保費(fèi)增速未能完全彌補(bǔ)人力下滑帶來的缺口。

三、轉(zhuǎn)型升級:從量變到質(zhì)變的必然選擇

面對行業(yè)發(fā)展困境,各保險(xiǎn)公司正積極推進(jìn)代理人隊(duì)伍轉(zhuǎn)型升級:

- 優(yōu)化隊(duì)伍結(jié)構(gòu),提高準(zhǔn)入門檻,吸引高素質(zhì)人才加入

- 加強(qiáng)專業(yè)培訓(xùn),提升代理人的專業(yè)知識(shí)和服務(wù)能力

- 推動(dòng)數(shù)字化賦能,利用科技手段提高展業(yè)效率

- 完善激勵(lì)機(jī)制,引導(dǎo)代理人關(guān)注長期價(jià)值和客戶服務(wù)

四、未來發(fā)展:質(zhì)量優(yōu)先成行業(yè)共識(shí)

保險(xiǎn)行業(yè)將更加注重發(fā)展質(zhì)量而非單純規(guī)模擴(kuò)張。代理人隊(duì)伍的質(zhì)態(tài)提升將成為決定公司競爭力的關(guān)鍵因素。在監(jiān)管趨嚴(yán)、客戶需求多元化的背景下,只有打造專業(yè)化、職業(yè)化的代理人隊(duì)伍,才能實(shí)現(xiàn)可持續(xù)發(fā)展。

2021年第一季度業(yè)績的“高開低走”為保險(xiǎn)行業(yè)敲響了警鐘。在行業(yè)轉(zhuǎn)型升級的關(guān)鍵時(shí)期,代理人質(zhì)態(tài)提升不僅是應(yīng)對當(dāng)前挑戰(zhàn)的應(yīng)急之策,更是推動(dòng)行業(yè)高質(zhì)量發(fā)展的長久之計(jì)。各保險(xiǎn)公司需在隊(duì)伍建設(shè)、產(chǎn)品創(chuàng)新、服務(wù)升級等方面持續(xù)發(fā)力,才能在激烈的市場競爭中立于不敗之地。